【導(dǎo)讀】如何在PCB的設(shè)計過程中,權(quán)衡利弊尋求一個合適的折中點,盡可能地減少這些干擾,甚至能夠避免部分電路的干涉,是射頻電路PCB設(shè)計成敗的關(guān)鍵。本文從PCB的LAYOUT角度,提供了一些處理的技巧,對提高射頻電路的抗干擾能力有較大的用處。

由于射頻(RF)電路為分布參數(shù)電路,在電路的實際工作中容易產(chǎn)生趨膚效應(yīng)和耦合效應(yīng),所以在實際的PCB設(shè)計中,會發(fā)現(xiàn)電路中的干擾輻射難以控制,如:數(shù)字電路和模擬電路之間相互干擾、供電電源的噪聲干擾、地線不合理帶來的干擾等問題。正因為如此,如何在PCB的設(shè)計過程中,權(quán)衡利弊尋求一個合適的折中點,盡可能地減少這些干擾,甚至能夠避免部分電路的干涉,是射頻電路PCB設(shè)計成敗的關(guān)鍵。文中從PCB的LAYOUT角度,提供了一些處理的技巧,對提高射頻電路的抗干擾能力有較大的用處。

1、RF布局

這里討論的主要是多層板的元器件位置布局。元器件位置布局的關(guān)鍵是固定位于RF路徑上的元器件,通過調(diào)整其方向,使RF路徑的長度最小,并使輸入遠(yuǎn)離輸出,盡可能遠(yuǎn)地分離高功率電路和低功率電路,敏感的模擬信號遠(yuǎn)離高速數(shù)字信號和RF信號。

在布局中常采用以下一些技巧。

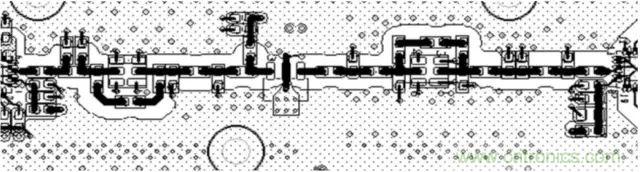

1.1 一字形布局

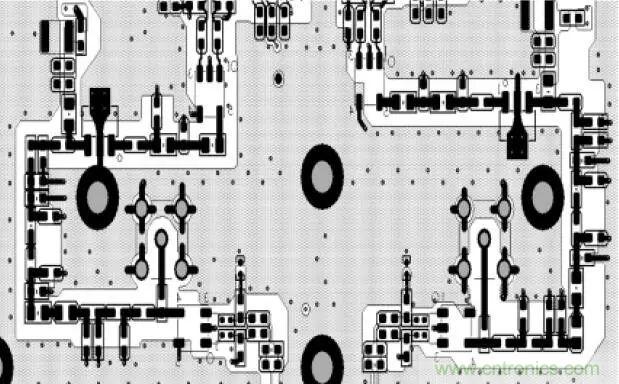

RF主信號的元器件盡可能采用一字形布局,如圖1所示。但是由于PCB板和腔體空間的限制,很多時候不能布成一字形,這時候可采用L形,最好不要采用U字形布局(如圖2所示),有時候?qū)嵲诒苊獠涣说那闆r下,盡可能拉大輸入和輸出之間的距離,至少1.5cm以上。

圖1 一字形布局

圖2 L形和U字形布局

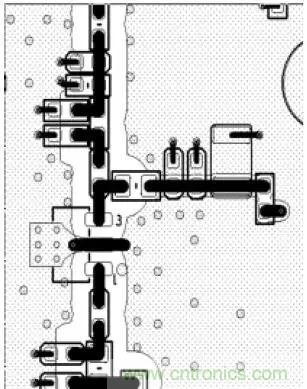

另外在采用L形或U字形布局時,轉(zhuǎn)折點最好不要剛進(jìn)入接口就轉(zhuǎn),如圖3左所示,而是在稍微有段直線以后再轉(zhuǎn),如圖3右圖所示。

圖3 兩種方案

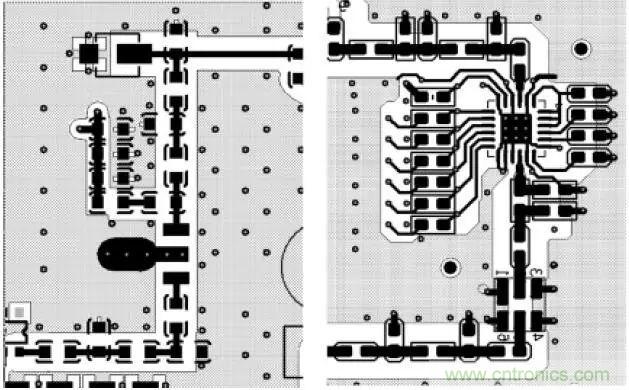

1.2 相同或?qū)ΨQ布局

相同的模塊盡可能做成相同的布局或?qū)ΨQ的布局,如圖4、圖5所示。

圖4 相同布局

圖5 對稱布局

1.3 十字形布局

偏置電路的饋電電感與RF通道垂直放置,如圖6所示,主要是為了避免感性器件之間的互感。

圖6 十字形布局

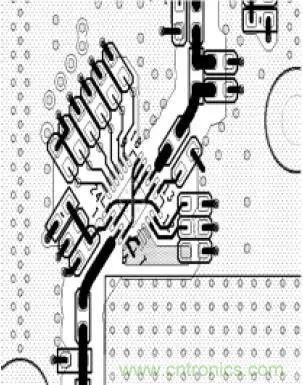

1.4 45度布局

為合理的利用空間,可以將器件45度方向布局,使射頻線盡可能短,如圖7所示。

圖7 45度布局

2、RF布線

布線的總體要求是:RF信號走線短且直,減少線的突變,少打過孔,不與其它信號線相交,RF信號線周邊盡量多加地過孔。

以下是一些常用的優(yōu)化方式:

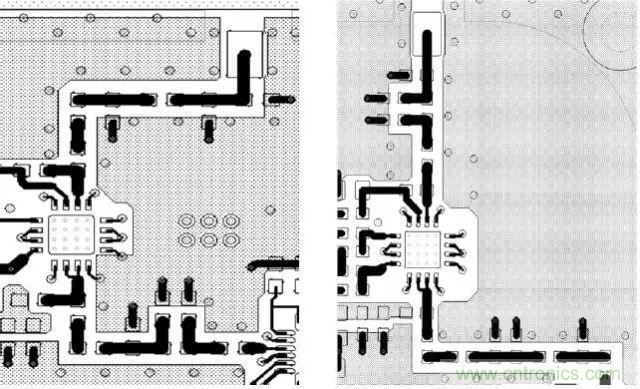

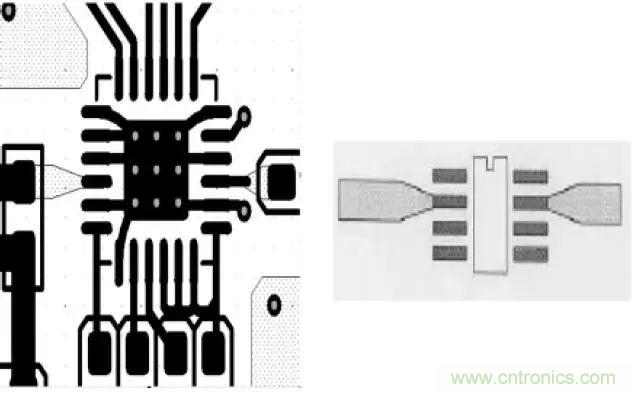

2.1 漸變線處理

在射頻線寬比IC器件管腳的寬度大比較多的情況下,接觸芯片的線寬采用漸變方式,如圖8所示。

圖8 漸變線

2.2 圓弧線處理

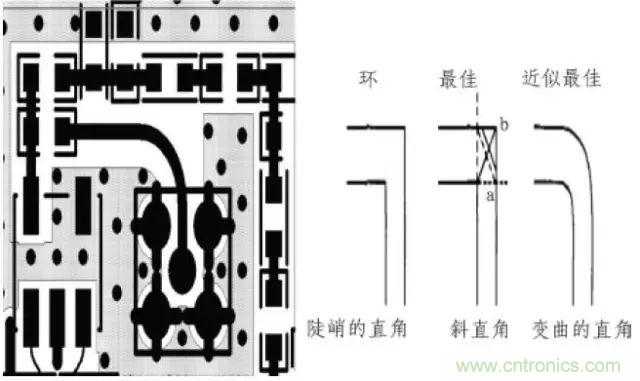

射頻線不能直的情況下,作圓弧線處理,這樣可以減少RF信號對外的輻射和相互問的耦合。有實驗證明,傳輸線的拐角采用變曲的直角,能最大限度的降低回?fù)p。如圖9所示。

圖9 圓弧線

2.3 地線和電源

地線盡可能粗。在有條件的情況下,PCB的每一層都盡可能的鋪地,并使地連到主地上,多打地過孔,盡量降低地線阻抗。

RF電路的電源盡量不要采用平面分割,整塊的電源平面不但增加了電源平面對RF信號的輻射,而且也容易被RF信號的干擾。所以電源線或平面一般采用長條形狀,根據(jù)電流的大小進(jìn)行處理,在滿足電流能力的前提下盡可能粗,但是又不能無限制的增寬。在處理電源線的時候,一定要避免形成環(huán)路。

電源線和地線的方向要與RF信號的方向保持平行但不能重疊,在有交叉的地方最好采用垂直十字交叉的方式。

2.4 十字交叉處理

RF信號與IF信號走線十字交叉,并盡可能在他們之間隔一塊地。

RF信號與其他信號走線交叉時,盡量在它們之間沿著RF走線布置一層與主地相連的地。如果不可能,一定要保證它們是十字交叉的。這里的其他信號走線也包括電源線。

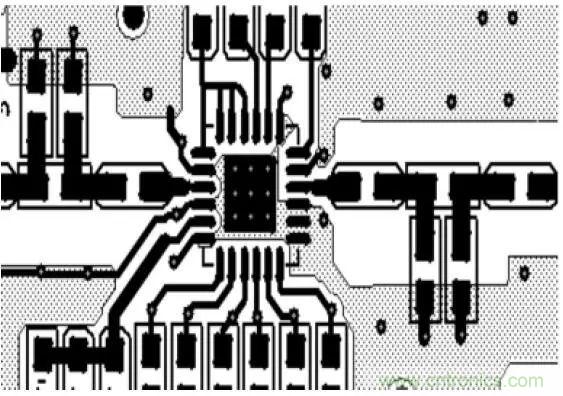

2.5 包地處理

對射頻信號、干擾源、敏感信號及其他重要信號進(jìn)行包地處理,這樣既可以提高該信號的抗干擾能力,也可以減少該信號對其他信號的干擾。如圖10所示。

圖10 包地處理

2.6 銅箔處理

銅箔處理要求圓滑平整,不允許有長線或尖角,若不能避免,則在尖角、細(xì)長銅箔或銅箔的邊緣處補幾個地過孔。

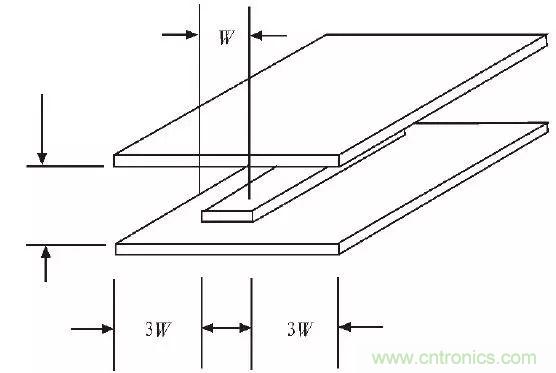

2.7 間距處理

射頻線離相鄰地平面邊緣至少要有3W的寬度,且3W范圍內(nèi)不得有非接地過孔。

圖11 間距

同層的射頻線要作包地處理,并在地銅皮上加地過孔,孔間距應(yīng)小于信號頻率所對應(yīng)波長(λ)的1/20,均勻排列整齊。包地銅皮邊緣離射頻線2W的寬度或3H的高度,H表示相鄰介質(zhì)層的總厚度。

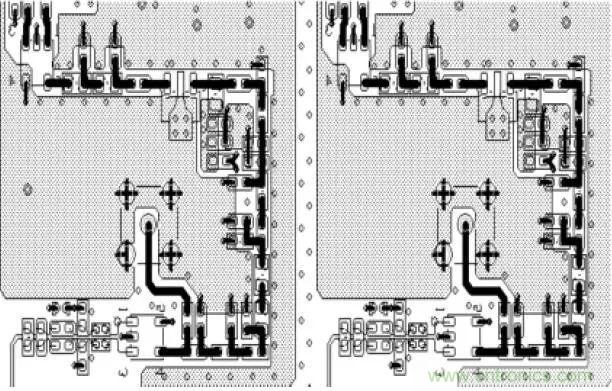

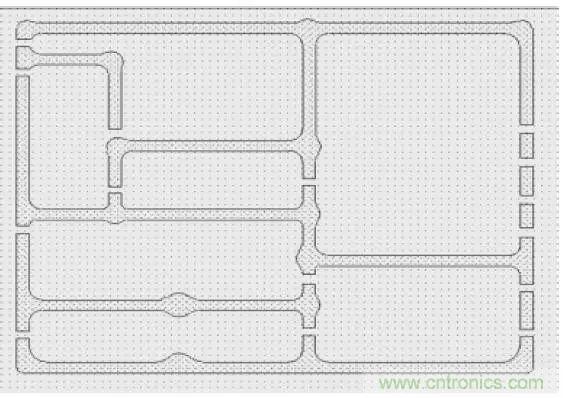

3、腔體處理

對整個RF電路,應(yīng)把不同模塊的射頻單元用腔體隔離,特別是敏感電路和強烈輻射源之間,在大功率的多級放大器中,也應(yīng)保證級與級之間的隔離。整個電路支流放置好后,就是對屏蔽腔的處理,屏蔽腔體的處理有以下注意事項:

整個屏蔽腔體盡量做成規(guī)則形狀,便于鑄模。對于每一個屏蔽腔盡量做成長方形,避免正方形的屏蔽腔。

屏蔽腔的轉(zhuǎn)角采用弧形,屏蔽金屬腔體一般采用鑄造成型,弧形的拐角便于鑄造成型時候拔模。如圖12所示。

圖12 腔體

屏蔽腔體的周邊是密封的,接口的線引入腔體一般采用帶狀線或微帶線,而腔體內(nèi)部不同模塊采用微帶線,不同腔體相連處采用開槽處理,開槽的寬度為3mm,微帶線走在正中間。

腔體的拐角放置3mm的金屬化孔,用來固定屏蔽殼,在每支長的腔體上也要均勻放置同等的金屬化孔,用來加固支撐作用。

腔體一般做開窗處理,便于焊接屏蔽殼,腔體上一般厚2 mm以上,腔體上加2排開窗過孔屏,過孔相互錯開,同一排過孔之間間距150MIL。

4、結(jié)束語

射頻電路PCB設(shè)計成敗的關(guān)鍵在于如何減少電路輻射,從而提高抗干擾能力,但是在實際的布局與布線中一些問題的處理是相沖突的,因此如何尋求一個折中點,使整個射頻電路的綜合性能達(dá)到最優(yōu),是設(shè)計者必須要考慮的問題。所有這些都要求設(shè)計者具有一定的實踐經(jīng)驗和工程設(shè)計能力,但是要具備這些能力,每一個設(shè)計者都不可能一蹴而就的,只有從其他人那里借鑒經(jīng)驗,加上自己的不停摸索和思考,才能不斷進(jìn)步。本文總結(jié)工作中的一些設(shè)計經(jīng)驗,有利于提高射頻電路PCB的抗干擾能力,幫助射頻電路設(shè)計初學(xué)者少走不必要的彎路。

PCB射頻電路四大基礎(chǔ)特性

此處將從射頻界面、小的期望信號、大的干擾信號、相鄰頻道的干擾四個方面解讀射頻電路四大基礎(chǔ)特性,并給出了在PCB設(shè)計過程中需要特別注意的重要因素。

射頻電路仿真之射頻的界面

無線發(fā)射器和接收器在概念上,可分為基頻與射頻兩個部份。基頻包含發(fā)射器的輸入信號之頻率范圍,也包含接收器的輸出信號之頻率范圍?;l的頻寬決定了數(shù)據(jù)在系統(tǒng)中可流動的基本速率?;l是用來改善數(shù)據(jù)流的可靠度,并在特定的數(shù)據(jù)傳輸率之下,減少發(fā)射器施加在傳輸媒介(transmission medium)的負(fù)荷。因此,PCB設(shè)計基頻電路時,需要大量的信號處理工程知識。發(fā)射器的射頻電路能將已處理過的基頻信號轉(zhuǎn)換、升頻至指定的頻道中,并將此信號注入至傳輸媒體中。相反的,接收器的射頻電路能自傳輸媒體中取得信號,并轉(zhuǎn)換、降頻成基頻。

發(fā)射器有兩個主要的PCB設(shè)計目標(biāo):第一是它們必須盡可能在消耗最少功率的情況下,發(fā)射特定的功率。第二是它們不能干擾相鄰頻道內(nèi)的收發(fā)機之正常運作。就接收器而言,有三個主要的PCB設(shè)計目標(biāo):首先,它們必須準(zhǔn)確地還原小信號;第二,它們必須能去除期望頻道以外的干擾信號;最后一點與發(fā)射器一樣,它們消耗的功率必須很小。

射頻電路仿真之大的干擾信號

接收器必須對小的信號很靈敏,即使有大的干擾信號(阻擋物)存在時。這種情況出現(xiàn)在嘗試接收一個微弱或遠(yuǎn)距的發(fā)射信號,而其附近有強大的發(fā)射器在相鄰頻道中廣播。干擾信號可能比期待信號大60~70 dB,且可以在接收器的輸入階段以大量覆蓋的方式,或使接收器在輸入階段產(chǎn)生過多的噪聲量,來阻斷正常信號的接收。如果接收器在輸入階段,被干擾源驅(qū)使進(jìn)入非線性的區(qū)域,上述的那兩個問題就會發(fā)生。為避免這些問題,接收器的前端必須是非常線性的。

因此,“線性”也是PCB設(shè)計接收器時的一個重要考慮因素。由于接收器是窄頻電路,所以非線性是以測量“交調(diào)失真(intermodulation distortion)”來統(tǒng)計的。這牽涉到利用兩個頻率相近,并位于中心頻帶內(nèi)(in band)的正弦波或余弦波來驅(qū)動輸入信號,然后再測量其交互調(diào)變的乘積。大體而言,SPICE是一種耗時耗成本的仿真軟件,因為它必須執(zhí)行許多次的循環(huán)運算以后,才能得到所需要的頻率分辨率,以了解失真的情形。

射頻電路仿真之小的期望信號

接收器必須很靈敏地偵測到小的輸入信號。一般而言,接收器的輸入功率可以小到1 μV。接收器的靈敏度被它的輸入電路所產(chǎn)生的噪聲所限制。因此,噪聲是PCB設(shè)計接收器時的一個重要考慮因素。而且,具備以仿真工具來預(yù)測噪聲的能力是不可或缺的。附圖一是一個典型的超外差(superheterodyne)接收器。接收到的信號先經(jīng)過濾波,再以低噪聲放大器(LNA)將輸入信號放大。然后利用第一個本地振蕩器(LO)與此信號混合,以使此信號轉(zhuǎn)換成中頻(IF)。前端(front-end)電路的噪聲效能主要取決于LNA、混合器(mixer)和LO。雖然使用傳統(tǒng)的SPICE噪聲分析,可以尋找到LNA的噪聲,但對于混合器和LO而言,它卻是無用的,因為在這些區(qū)塊中的噪聲,會被很大的LO信號嚴(yán)重地影響。

小的輸入信號要求接收器必須具有極大的放大功能,通常需要120 dB這么高的增益。在這么高的增益下,任何自輸出端耦合(couple)回到輸入端的信號都可能產(chǎn)生問題。使用超外差接收器架構(gòu)的重要原因是,它可以將增益分布在數(shù)個頻率里,以減少耦合的機率。這也使得第一個LO的頻率與輸入信號的頻率不同,可以防止大的干擾信號“污染”到小的輸入信號。

因為不同的理由,在一些無線通訊系統(tǒng)中,直接轉(zhuǎn)換(direct conversion)或內(nèi)差(homodyne)架構(gòu)可以取代超外差架構(gòu)。在此架構(gòu)中,射頻輸入信號是在單一步驟下直接轉(zhuǎn)換成基頻,因此,大部份的增益都在基頻中,而且LO與輸入信號的頻率相同。在這種情況下,必須了解少量耦合的影響力,并且必須建立起“雜散信號路徑(stray signal path)”的詳細(xì)模型,譬如:穿過基板(substrate)的耦合、封裝腳位與焊線(bondwire)之間的耦合、和穿過電源線的耦合。

射頻電路仿真之相鄰頻道的干擾

失真也在發(fā)射器中扮演著重要的角色。發(fā)射器在輸出電路所產(chǎn)生的非線性,可能使傳送信號的頻寬散布于相鄰的頻道中。這種現(xiàn)象稱為“頻譜的再成長(spectral regrowth)”。在信號到達(dá)發(fā)射器的功率放大器(PA)之前,其頻寬被限制著;但在PA內(nèi)的“交調(diào)失真”會導(dǎo)致頻寬再次增加。如果頻寬增加的太多,發(fā)射器將無法符合其相鄰頻道的功率要求。當(dāng)傳送數(shù)字調(diào)變信號時,實際上,是無法用SPICE來預(yù)測頻譜的再成長。因為大約有1000個數(shù)字符號(symbol)的傳送作業(yè)必須被仿真,以求得代表性的頻譜,并且還需要結(jié)合高頻率的載波,這些將使SPICE的瞬態(tài)分析變得不切實際。

推薦閱讀: