【導(dǎo)讀】AD717x是ADI最新系列的精密Σ-Δ型ADC。該ADC系列是市場(chǎng)上第一個(gè)提供真正24位無噪聲輸出的轉(zhuǎn)換器系列。AD717x器件可使對(duì)噪聲異常敏感的儀器儀表電路的動(dòng)態(tài)范圍最大化,支持降低或消除信號(hào)調(diào)理級(jí)中的前置放大器增益。這些器件還能高速運(yùn)行,提供比以前更短的建立時(shí)間。由此可縮短控制環(huán)路對(duì)輸入激勵(lì)信號(hào)的響應(yīng)時(shí)間,或通過更快的每通道吞吐速率來提高轉(zhuǎn)換通道密度。

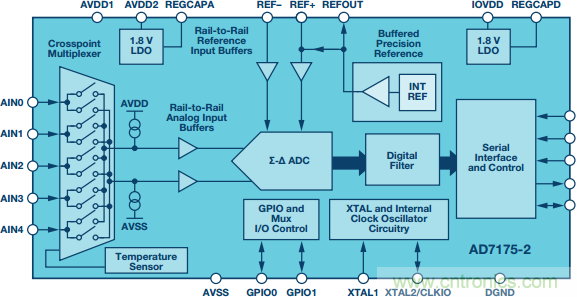

AD717x頁面提供了完整系列的詳細(xì)信息,包括有關(guān)AD7172-2、AD7175-2、AD7172-4、AD7173-8和AD7175-8的信息。這些精密ADC具有完全集成的模擬信號(hào)鏈,包括真軌到軌模擬輸入和基準(zhǔn)輸入緩沖器。該系列提供多種輸入通道數(shù),不同器件可通過引腳對(duì)應(yīng)方式升級(jí)為其他轉(zhuǎn)換速度或更低噪聲/功耗的器件。AD7175-2和AD7175-8提供最快的吞吐速率和最低的噪聲。AD7177-2提供32位分辨率輸出。AD7172和AD7173提供最低功耗選項(xiàng)。

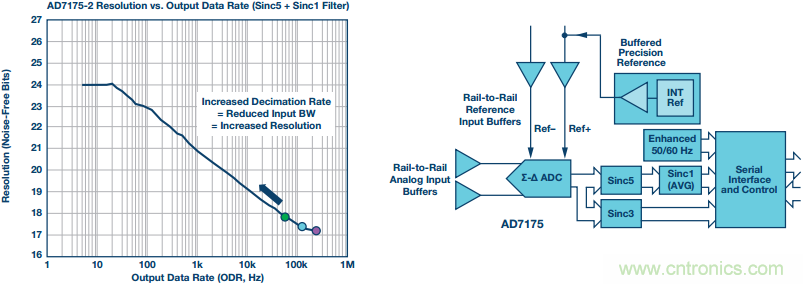

圖1. AD7175x Σ-Δ ADC系列;AD7175-2框圖和噪聲性能

AD7175-2具有一個(gè)非常有用的軟件工具來幫助評(píng)估。Eval+是一個(gè)單一軟件,可從ADI網(wǎng)站下載,用來在有或沒有硬件的情況下配置、分析、選擇ADC。該軟件與硬件一起運(yùn)行時(shí),會(huì)像標(biāo)準(zhǔn)評(píng)估板那樣工作。無硬件時(shí),ADC的功能模型在后臺(tái)運(yùn)行,支持用戶為其終端應(yīng)用建立最佳工作配置。

圖2. AD7175-2 Eval+軟件在功能模型評(píng)估模式下的配置選項(xiàng)卡

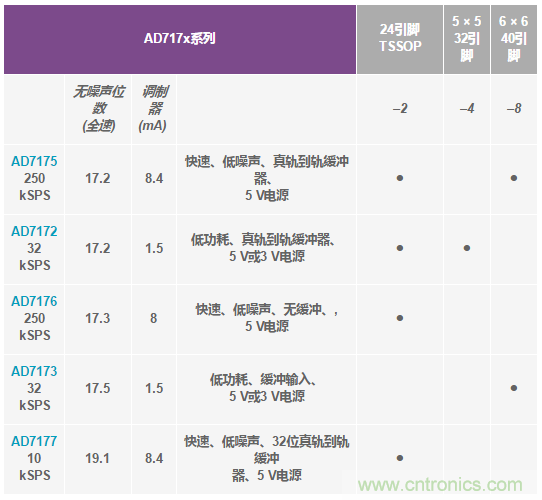

表1. AD717x系列概覽,顯示了可用的通道數(shù)選項(xiàng)和系列成員的引腳對(duì)應(yīng)情況

消除Σ-Δ ADC量化噪聲:噪聲和帶寬考慮因素

使用AD7175 ADC來說明如何利用數(shù)字濾波消除Σ-Δ型ADC的量化噪聲。關(guān)鍵在于噪聲/輸入帶寬和建立時(shí)間的權(quán)衡分析。

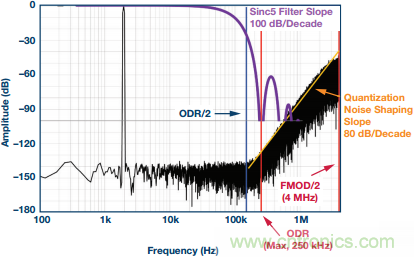

圖4顯示了調(diào)制器原始噪聲來源與AD7175器件從DC到FMOD/2 (或4 MHz)的頻率對(duì)數(shù)的關(guān)系。AD7175調(diào)制器以8 MHz (FMOD)的有效速率采樣。調(diào)制器為MASH型,對(duì)調(diào)制器噪聲提供80 dB/十倍頻程的衰減速率。電路的熱噪聲決定了調(diào)制器噪聲開始以斜坡變化之前頻帶內(nèi)的噪底。從顯示低噪底的曲線可以看出該ADC對(duì)低帶寬信號(hào)的高動(dòng)態(tài)范圍能力。此動(dòng)態(tài)范圍以及AD7175降低噪底的能力可用來改善應(yīng)用的靈敏度,這在采集低幅度信號(hào)時(shí)特別有用。

ADC的最低過采樣比、數(shù)字濾波器階數(shù)和轉(zhuǎn)折頻率都有助于確保量化噪聲不是ADC噪聲的限制因素。為了濾除噪聲,濾波器0ca7d2的包絡(luò)必須能夠以足夠大的滾降速率進(jìn)行衰減,從而應(yīng)對(duì)幅度量化噪聲的增速。

AD7175的最低過采樣比為×32,在8 MHz FMOD條件下,最大輸出數(shù)據(jù)速率為250 kHz。

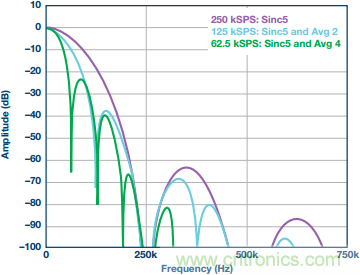

AD7175提供了多種不同類型的濾波器,可供用戶選擇。數(shù)字濾波器的工作原理是通過比較不同情況下的sinc5 + sinc1和sinc3濾波器來說明的。

在250 kHz ODR時(shí),AD7175 sinc5 + sinc1可直接配置為sinc5,其−3 dB頻率為~0.2 × ODR (50 kHz)。sinc5濾波器的衰減包絡(luò)為−100 dB/十倍頻程。這意味著sinc5濾波器的衰減和滾降速率足以消除調(diào)制器噪聲,如圖3所示。

圖3. AD7175調(diào)制器輸出頻譜DC至FMOD/2,采用sinc5 + sinc1和32倍抽取(產(chǎn)生sinc5直流響應(yīng))

圖4. AD7175-2 sinc5 + sinc1濾波器:通過更改ADC抽取率來調(diào)整輸入帶寬

相比之下,若更改為250 kHz ODR的sinc3,衰減和滾降速率將不足以消除調(diào)制器噪聲。數(shù)據(jù)手冊(cè)中的250 kHz和125 kHz ODR時(shí)的噪聲數(shù)值說明了這一情況。只有將數(shù)據(jù)速率設(shè)置為62.5 kHz或更低,sinc3響應(yīng)才能完全濾除ADC結(jié)果中的量化噪聲。

除了濾除量化噪聲以外,數(shù)字濾波器還能通過調(diào)整輸入帶寬來降低噪聲。這是通過提高抽取率實(shí)現(xiàn)的。對(duì)于sinc5 + sinc1濾波器,提高過采樣比意味著初始五階sinc濾波器要進(jìn)行均值計(jì)算。利用初始結(jié)果的均值,用戶可以選擇不同的輸出數(shù)據(jù)速率、速度和帶寬來改善噪聲性能(如圖5所示),即先由sinc5再由sinc5 + sinc1求均值來改善噪聲性能。對(duì)sinc5結(jié)果求均值會(huì)引入頻率為輸出數(shù)據(jù)速率及其倍數(shù)的一階陷波,這些陷波會(huì)與sinc5總包絡(luò)復(fù)合。sinc型濾波器中的陷波頻率傳統(tǒng)上是用來抑制已知頻率的干擾信號(hào),即通過把數(shù)據(jù)速率策略性地設(shè)置為與干擾頻率重合。一個(gè)經(jīng)典例子是50 Hz和60 Hz的工頻抑制。

圖5. AD7175-2 sinc5 + sinc1濾波器 – 噪聲與ODR的關(guān)系

sinc型濾波器是具有sin(x)/x剖面的移動(dòng)平均濾波器,因此一般稱其為sinc濾波器。該濾波器由一系列積分器、一個(gè)用作抽取率的開關(guān)和一系列微分器組成。它是一種有限脈沖響應(yīng)(FIR)型濾波器。對(duì)于輸入的階躍變化,它表現(xiàn)出已知且有限的線性相位響應(yīng)。深陷波發(fā)生在輸出數(shù)據(jù)速率及其整數(shù)倍處,陷波內(nèi)的信號(hào)會(huì)被衰減。

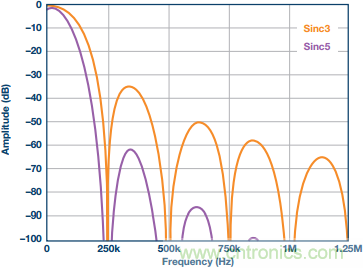

圖6比較了AD7175的三階和五階sinc濾波器,二者均以32倍抽取率運(yùn)行。這種情況下,兩個(gè)濾波器均以250 kHz的輸出速率提供轉(zhuǎn)換數(shù)據(jù)。濾波器的階數(shù)決定滾降速率和−3 dB頻率。sincP濾波器位于–P × 20 dB/十倍頻程的頻率響應(yīng)包絡(luò)之下。滾降越陡,−3 dB頻率越低。不同階數(shù)濾波器之間的主要區(qū)別在于濾波器建立時(shí)間,根據(jù)情況不同,其對(duì)終端測(cè)量應(yīng)用的影響也不同。

圖6. 不同階數(shù)sinc濾波器的頻域比較:sinc5與sinc3

濾波器建立時(shí)間

當(dāng)數(shù)字濾波器處理來自Σ-Δ調(diào)制器的數(shù)據(jù)流的移動(dòng)平均值時(shí),存在一個(gè)相關(guān)的建立時(shí)間。該延遲對(duì)所有FIR濾波器是固定的,但對(duì)不同階數(shù)的sinc濾波器,該延遲是不同的。通常用兩項(xiàng)來描述該延遲:群延遲和建立時(shí)間。群延遲描述從輸入端存在模擬信號(hào)到在數(shù)字輸出端看到它的延遲時(shí)間。例如,對(duì)于單音正弦波,群延遲就是從模擬輸入端存在該正弦波電壓峰值到該峰值出現(xiàn)在數(shù)字輸出端的時(shí)間差。

建立時(shí)間是指數(shù)字濾波器的全部均值時(shí)間。如果模擬輸入端有一個(gè)階躍,那么需要經(jīng)過濾波器的完全建立時(shí)間,ADC的數(shù)據(jù)輸出才與階躍之前的輸入無關(guān)。還可能存在其他延遲,如濾波器的計(jì)算時(shí)間等。對(duì)于AD7175系列,第一次轉(zhuǎn)換會(huì)有較長(zhǎng)的建立時(shí)間;由于初始計(jì)算周期為1/ODR,離開待機(jī)狀態(tài)后的建立也可能引起延遲。除濾波器建立時(shí)間之外的延遲可能依選擇的轉(zhuǎn)換器不同而異,因此,閱讀ADC數(shù)據(jù)手冊(cè)時(shí)應(yīng)留心。

通過比較單一Σ-Δ ADC與多路復(fù)用Σ-Δ ADC,可以更好地說明濾波器建立時(shí)間影響。數(shù)字濾波器的建立時(shí)間會(huì)嚴(yán)重影響多個(gè)輸入通道循環(huán)轉(zhuǎn)換的速率,因?yàn)橐3指魍ǖ赖慕Y(jié)果獨(dú)立。

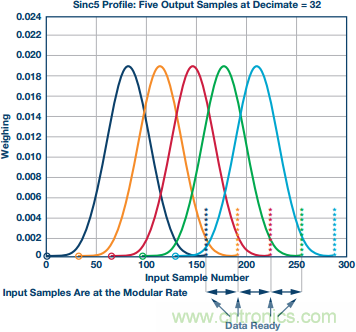

為什么要等待完全建立時(shí)間之后才能給出獨(dú)立結(jié)果?讓我們看看采用單一輸入源的單通道ADC的數(shù)字濾波。來自Σ-Δ ADC調(diào)制器的數(shù)據(jù)以FMOD的速率傳送到數(shù)字濾波器(如圖5所示),每個(gè)樣本都通過移動(dòng)平均濾波器。根據(jù)階數(shù)和類型不同,濾波器在轉(zhuǎn)換期間(由濾波器抽取率設(shè)置)內(nèi)以不同方式衡量各樣本,如圖 7所示。

輸入樣本0和隨后的樣本是調(diào)制器在其每個(gè)時(shí)鐘周期的離散輸出結(jié)果。y軸表示數(shù)字濾波器衡量各樣本而給出的權(quán)重比例。此權(quán)重的形狀就是低通數(shù)字濾波器的時(shí)域表示。這種情況下的輸出數(shù)據(jù)速率為250 kHz (8 MHz/32 = FMOD/抽取率)。數(shù)據(jù)就緒信號(hào)(各種顏色的豎直虛線)之間的時(shí)間為4 μs。ADC采用sinc5 + sinc1濾波器和32倍抽取率運(yùn)行。在定義濾波器輸出為調(diào)制器的模擬輸入時(shí),所有五個(gè)轉(zhuǎn)換輸出都有一定的重疊,因此,沒有輸出是各自獨(dú)立的。對(duì)于單一ADC輸入,各轉(zhuǎn)換結(jié)果共享調(diào)制器模擬輸入,但濾波器以不同權(quán)重衡量各調(diào)制器輸出。

圖7. 單一ADC輸入、sinc5和五個(gè)轉(zhuǎn)換輸出周期

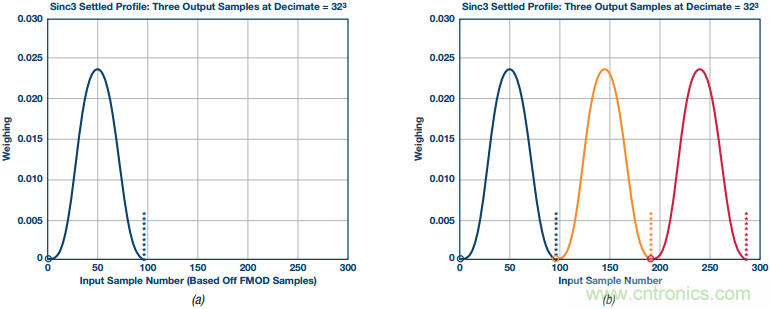

對(duì)于多路復(fù)用輸入情況,調(diào)制器產(chǎn)生的每個(gè)轉(zhuǎn)換數(shù)據(jù)對(duì)各通道必須是獨(dú)立的。必須經(jīng)過濾波器的完全建立時(shí)間之后,多路復(fù)用器才能從一個(gè)模擬輸入通道切換到另一個(gè)模擬輸入通道。以sinc3型濾波器為例,使用32倍抽取率,一次轉(zhuǎn)換的濾波器建立時(shí)間如圖8(a)所示。一旦濾波器完全建立,數(shù)據(jù)輸出便是先前96 個(gè)調(diào)制器輸出的加權(quán)平均值。這相當(dāng)于12 μs或三個(gè)周期的ADC輸出數(shù)據(jù)速率。

圖8(b)顯示了多路復(fù)用情況的前三個(gè)樣本,ADC輸出的各樣本均已完全建立。在任何樣本之間,調(diào)制器輸出都沒有重疊。DRDY(豎直線)之間的時(shí)間所指示的復(fù)用速率由濾波器的建立時(shí)間決定。此速率在數(shù)據(jù)手冊(cè)和性能曲線中常常是作為完全建立數(shù)據(jù)速率來描述。

圖8. 多路復(fù)用ADC、sinc3濾波器和三個(gè)轉(zhuǎn)換周期—完全建立的數(shù)據(jù)

對(duì)于sincP濾波器,濾波器的建立時(shí)間為濾波器階數(shù)P乘以1/ODR。對(duì)于以250 kHz ODR運(yùn)行的sinc3濾波器,其建立時(shí)間為3 ×1/250 kHz = 12 μs。作為比較,若使用sinc5濾波器,ODR同為250 kHz,則建立時(shí)間為5 × (1/2 50 kHz) = 20 μs。

近似的通道切換速率為ODR除以濾波器階數(shù),也就是ODR/3 (對(duì)于sinc3濾波器)或ODR/5 (對(duì)于sinc5濾波器)。對(duì)于直接sinc濾波器,這是很顯然的。對(duì)于sinc5 + sinc1型濾波器,需要增加一個(gè)步驟。AD7175系列ADC允許選擇不同類型的濾波器。下一部分將介紹不同類型濾波器之間的區(qū)別,并提供一個(gè)例子來說明如何計(jì)算各種情況下的建立時(shí)間。

現(xiàn)在看看多路復(fù)用情況下的建立時(shí)間。在過程控制和工廠自動(dòng)化中,典型的模擬輸入模塊會(huì)有一個(gè)前端調(diào)理,用以將±10 V輸入調(diào)整到AD7175-8的輸入范圍內(nèi)。然后,AD7175-8會(huì)復(fù)用各通道,按順序轉(zhuǎn)換各輸入或輸入對(duì)。完成所有通道轉(zhuǎn)換的時(shí)間取決于所用的濾波器和通道數(shù)目。

下例對(duì)使用sinc3濾波器和使用sinc5 + sinc1濾波器進(jìn)行了比較,二者配置為相同的輸出數(shù)據(jù)速率,我們會(huì)看到建立時(shí)間計(jì)算的對(duì)比和方法。用戶可以選擇AD7175-8的這兩個(gè)濾波器選項(xiàng)。

a. 使用sinc3濾波器,62.5 kHz ODR 計(jì)算建立時(shí)間。

?AD7175 sinc3: ODR = 62.5 kHzz

?建立時(shí)間 = 3 × (1/62.5 kHz) = 48 μs

?通道開關(guān)速率 = 1/48 μs = 20.833 kHz

b. 使用sinc5 + sinc1濾波器,62.5 kHz ODR 計(jì)算建立時(shí)間。

? AD7175 sinc5 + sinc1: ODR = 62.5 kHz

注意有兩個(gè)部分。sinc5濾波器在4 μs窗口上求均值(FMOD = 8 MHz),因此它以250 kHz的速率將數(shù)據(jù)傳送到均值模塊。

1.sinc5的建立時(shí)間 = 5 × 1/250 kHz = 20 μs。

?這提供均值計(jì)算的第一個(gè)樣本。

2.sinc1的建立,均值濾波器。

?對(duì)于ODR = 62.5 kHz,250 kHz數(shù)據(jù)流四次求均值。

?用于均值計(jì)算的剩余三個(gè)樣本的建立

?時(shí)間為3 × 1/250 kHz = 12 μs。

?總建立時(shí)間 = 20 μs + 12 μs = 32 μs,

?通道開關(guān)速率 = 1/32 μs = 31.25 kHz。

注意:對(duì)于sinc5 + sinc1濾波器,當(dāng)數(shù)據(jù)速率為10 kSPS及以下時(shí),ADC具有單周期建立特性。這意味著ADC的建立時(shí)間為1/ODR。

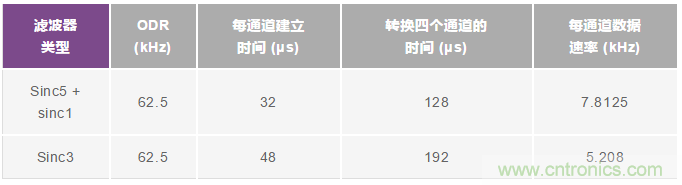

表2顯示了采用設(shè)置(a)和(b)的4通道多路復(fù)用測(cè)量的比較。使用sinc5 + sinc1濾波器可提高每通道采樣速率,說明較短建立時(shí)間有優(yōu)勢(shì)。注意:這個(gè)經(jīng)驗(yàn)法則僅適用于轉(zhuǎn)換器,若各路輸入之前有模擬預(yù)調(diào)理電路,并且其時(shí)間常數(shù)比ADC要長(zhǎng),那么起主導(dǎo)作用的將是最差情況建立時(shí)間。

表2顯示了比較結(jié)果:

表2. 對(duì)于一個(gè)4通道多路復(fù)用系統(tǒng)(例如采用AD7175-8),Sinc5 + Sinc1與Sinc3濾波器的每通道數(shù)據(jù)速率比較

以上就是對(duì)Σ-Δ型ADC的簡(jiǎn)要介紹—圍繞調(diào)制器的原理,數(shù)字濾波的概念和例子,以及其在測(cè)量系統(tǒng)內(nèi)對(duì)噪聲、建立時(shí)間的影響和一些連鎖效應(yīng)。

推薦閱讀: